You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

BRN Discussion Ongoing

- Thread starter TechGirl

- Start date

Evermont

Stealth Mode

BrainChip still listed on the Eastronics page.

I have changed my opinion. I am guessing with Renesas, Arm and SiFive now that has been superseded.I thought the reason Eastronics was a “Channel Partner” was to service Israel clients.

My understanding was that Israel is extremely technologically advanced, and I think was the birth place of Nanose so there was an avenue for the technology to be distributed from there. I am guessing with Renesas, Arm and SiFive now that has been superseded.

Taproot

Regular

Francios Piednoel was known in the tech industry as " Mr Intel "I may be fooling myself but the only IP in the known commercial world that could possibly be 100x more efficient than a GPU is AKIDA 2.0.

We all know Tech here and one thing he does very well is to send congratulations via email to the people at Brainchip who make things happen.

The podcast with Prophesee was one such happening and he sent Rob Telson a congratulations for all his hard work on behalf of shareholders and the company.

Rob Telson replied thanking Tech for his kind words. In the process he described AKIDA as ‘amazing technology’.

It is human nature to become familiar with what we see everyday and this familiarity normally removes the wonder.

As a result these words struck me as Rob Telson has been with Brainchip for quite some years now exposed every day to AKIDA technology and yet uses these words.

There is in my mind no doubt that the amazing technology IP that is said to have ended the Era of GPU4ML can be none other than AKIDA 2.0.

My very anonymous opinion only so as usual DYOR

FF

AKIDA BALLISTA

He left Intel in 2017 to go work for Mercedes, so he must be intimately involved in the Brainchip / Mercedes partnership.

So seems to be hinting at something a little more advanced than Akida 1.0

Very exciting tweet, thanks to @chapman89

Learning

Learning to the Top 🕵♂️

As I want to do some research on 'Neuromorphic Revolution' to learn more about the changing tide of of the current computing climate. Many great articles came up.(all 3 mentioned Brainchip, 1 from 2019)

www.eejournal.com

www.eejournal.com

“This is where we get excited. You’ll see a lot of these functionalities in vehicles—recognition of voices, faces, and individuals in the vehicle. This allows the vehicles to have customisation and device personalisation according to the drivers or the passengers as well,” says Telson. These really are exciting times.

www.electronicsforu.com

www.electronicsforu.com

I may have missed, but don't remember those words from Rob Telson. What an exciting time ahead for being a shareholder.

As for the 'WANCA' they wouldn't know the difference between a soy sauce and a fish sauce. If they are blindside by this Neuromorphic Revolution of Akida the 'antidote'. I say good luck to them; sleeping on the park bench. While all us shareholders get invited to cruise on the 'Allure of the Seas' with Captain FF.

It's great to be a shareholder 🏖

Neuromorphic Revolution

According to tech folklore, Carver Mead actually coined the term “Moore’s Law” – some ten years or so after the publication of Gordon Moore’s landmark 1965 Electronics Magazine article “Cramm…

“This is where we get excited. You’ll see a lot of these functionalities in vehicles—recognition of voices, faces, and individuals in the vehicle. This allows the vehicles to have customisation and device personalisation according to the drivers or the passengers as well,” says Telson. These really are exciting times.

What’s So Exciting About Neuromorphic Computing

The human brain is the most efficient and powerful computer that exists. Even after decades and decades of technological advancements, no computer has managed to beat the brain with respect to efficiency, power consumption, and many other factors.

I may have missed, but don't remember those words from Rob Telson. What an exciting time ahead for being a shareholder.

As for the 'WANCA' they wouldn't know the difference between a soy sauce and a fish sauce. If they are blindside by this Neuromorphic Revolution of Akida the 'antidote'. I say good luck to them; sleeping on the park bench. While all us shareholders get invited to cruise on the 'Allure of the Seas' with Captain FF.

It's great to be a shareholder 🏖

TheFunkMachine

seeds have the potential to become trees.

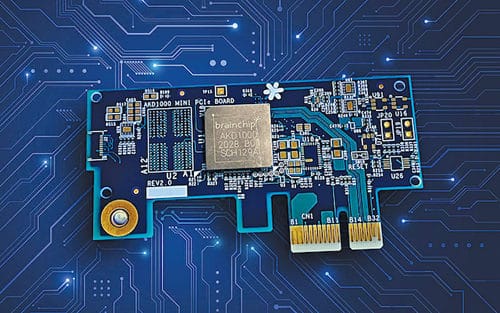

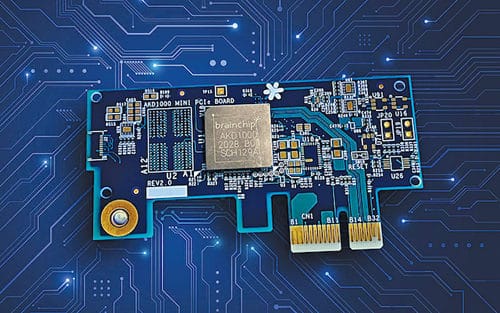

I have a really good feeling about this being Akida IP. If it is 1.0 or 2.0 doesn’t matter to me, but I would guess 1.0 as we know Mercedes has had their hands on that for a while now. Please Mercedes give us another market boost and name drop us for all to seeWorks for Mercedes. I wonder who he is referring to?! If it was Brainchip you would imagine that they’ve “reviewed” the IP a while ago, unless they have the new and improved akida containing LSTM?? View attachment 17989

JoMo68

Regular

I feel that Mike Davies, if indeed he is quoted accurately, is being quite disingenuous in that article…I find the title quite distracting. It seems to indicate the hardware is not important. Whereas, in fact, the hardware is of prime importance.

Sure, software will drive adoption, but the software can do nothing in the absence of the hardware. And yes, the hardware might be pretty to look at, but is useless if not put to any real world use. This is the problem I see with the lack of market acceptance of Brainchip, but us investors know the potential of Akida and just need to wait for that potential to be realized in real world products so others can also see it.

The following extract paints a more appropriate picture:

"while the hardware is important for bringing quantum and neuromorphic life to life, what will drive adoption is the accompanying software. Systems are nice to look at, but they are decorations if organizations can’t use them."

With that statement I agree whole heatedly. I have been vocal in stating that end users are struggling to understand the use cases for neuromorphic and quantum computing. Entrepreneurs are struggling to work out how they will make money out of these technologies. People are struggling to even pronounce the words. But then, end users don't need to understand the technologies. We just need some smart people (who do understand them) to create devices that become indispensable, and the rest will be history. And yes, along with the crucial underlying hardware, it will be software that brings that hardware to a real world gadget.

ANY technology could have the very same article written about it. People use microwave ovens every day but don't need to understand how the microwaves are generated, what a microwave is, how microwaves heat food, or why microwaves cook faster than a conventional oven. They don't even need to know how pressing a button on the panel communicates that instruction to the oven. But still they press the button, watch the food turn, and wait for the "ping" sound.

I see no difference in the need, nor the desire, for the average person on the street to understand quantum or neuromorphic computing, but one day in the not too distant future, we all will be using devices that utilize them, and yes that utilization is through software interacting with the hardware. The end users need understand nothing about either.

Adopting a technology is all about perceiving its usefulness, it's all about having a handy gadget that does something the user needs or wants.

JoMo68

Regular

I’m planning my beach front property already…Just start by googling shit that you can’t afford… that’s what I do

You do beach and I’ll go countryside and we can share the love!I’m planning my beach front property already…

Fullmoonfever

Top 20

Big bonus if is indeed Akida 1.5 / 2.0 and although no factual evidence as yet I would expect that if the company has indeed released it into the wild for end user testing that we would see a mkt update or something maybe with the 4C if really lucky

Considering they have identified the next Akida evolutions in previous pressos imo it would be a milestone event for an achievement the mkt should know about even if MB wasn't mentioned.

Considering they have identified the next Akida evolutions in previous pressos imo it would be a milestone event for an achievement the mkt should know about even if MB wasn't mentioned.

Hi SG,Thanks Jesse,

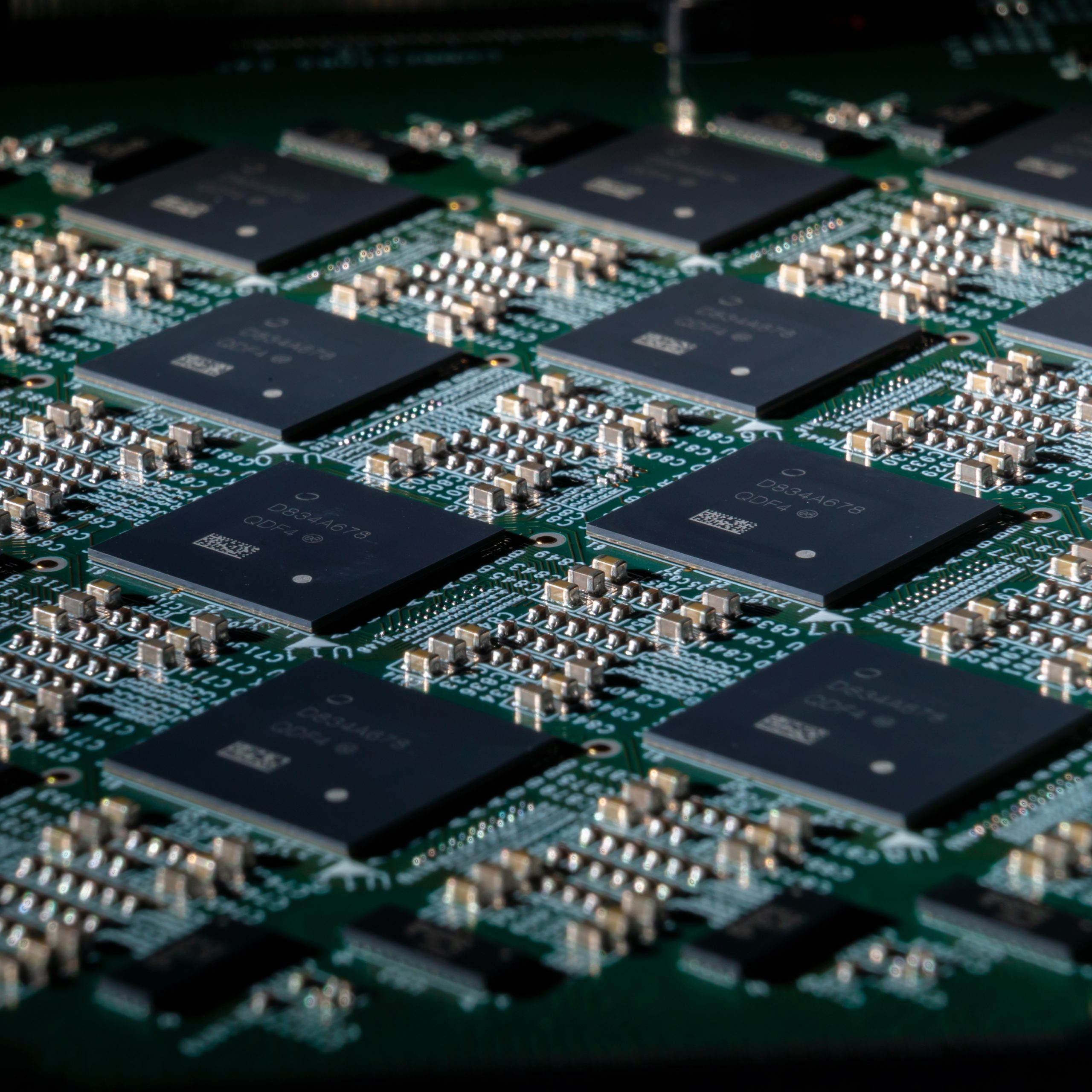

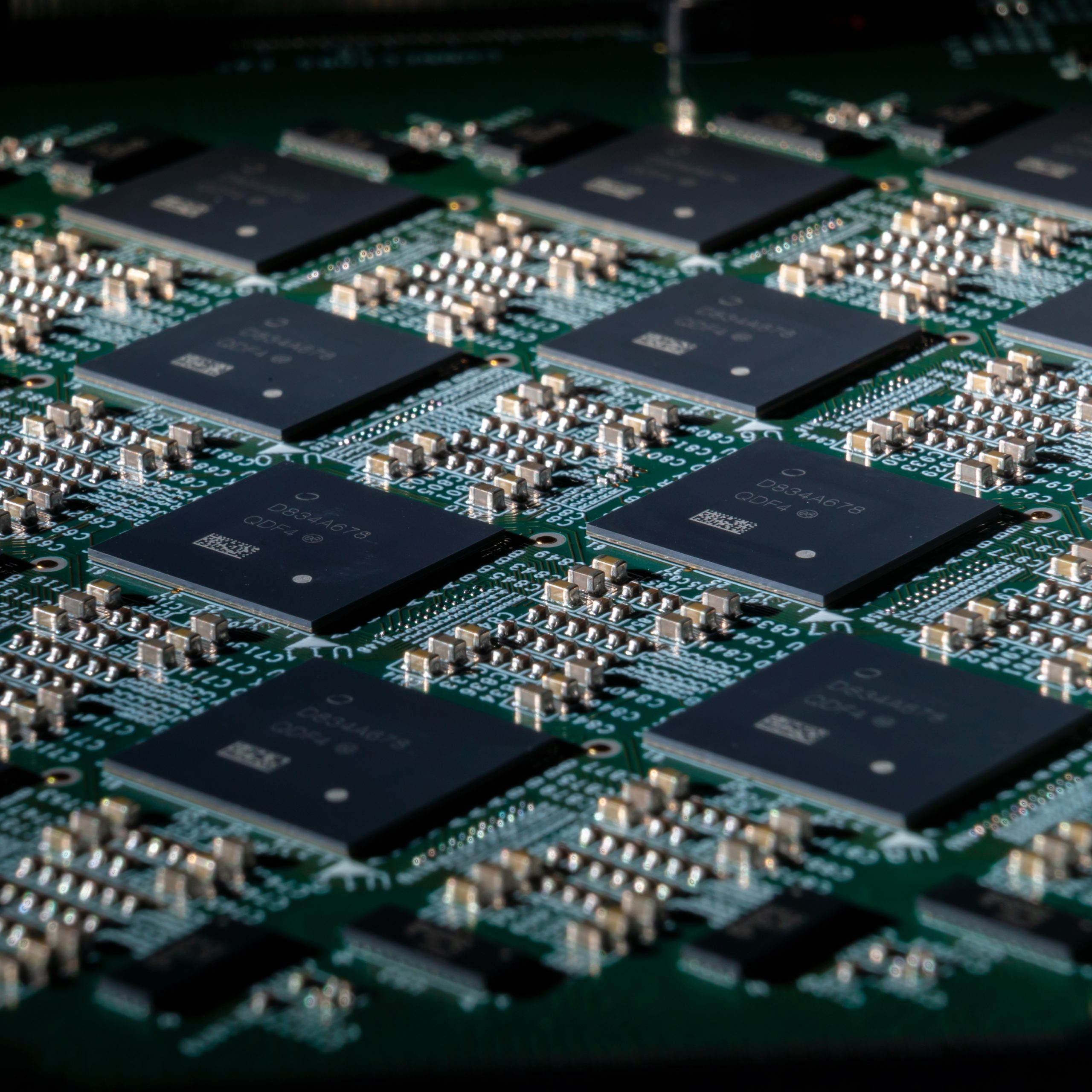

The image automatically says Brain-Chip to me however a lot of companies are using similar images. Hope it is us of course!

I looked him up and don’t have the knowledge to understand another post of his 16 hrs ago:

View attachment 17994

And the conversation following it is interesting but over my head too!

View attachment 17995

Can anyone @Diogenese help me in understanding the conversation please?

Edit: sorry, missed some of the conversation:

View attachment 17996

Now you're seeking the forbidden fruit of the Tree of Knowledge.

My serpentine explanation is that ordinary CMOS transistors are built up in layers parallel to the surface of the silicon wafer.

That is, the area of the gate, source, and drain of a field effect transistor (FET) are parallel to the surface, and the thickness is vertical to the surface.

As the density of the CMOS chips reached the limit of the technology (More's law about doubling the number of chips every couple of years), chip engineers needed to find new ways of increasing the number of transistors per wafer.

In a FINFET, the transistor is tipped on its side so the area is vertical to the surface, and the thickness occupies an area of the surface. Because the area is much larger than the thickness, this allows more transistors to be packed in.

Then we got "gate-all-around" (GAA) transistors which improved the performance of the transistors.

https://semiengineering.com/knowledge_centers/integrated-circuit/transistors/3d/gate-all-around-fet/

As the fin width in a finFET approaches 5nm, channel width variations could cause undesirable variability and mobility loss. One promising and futuristic transistor candidate — gate-all-around FET — could circumvent the problem. Considered the ultimate CMOS device in terms of electrostatics, gate-all-around is a device in which a gate is placed on all four sides of the channel. It’s basically a silicon nanowire with a gate going around it.

The comments refer to CFET, which is Complementary FET, a more complex GAA-FET.

https://semiengineering.com/knowled... transistor stacks n-type wires on each other.

Slated for 2.5nm and beyond, complementary FET (CFET) is a more complex version of a gate-all-around device. Traditional gate-all-around FETs stack several p-type wires on top of each other. In a separate device, the transistor stacks n-type wires on each other.

In CFETs, the idea is to stack both nFET and pFET wires on each other. A CFET could stack one nFET on top of a pFET wire, or two nFETs on top of two pFET wires. This ‘folding’ of the nFET and pFET eliminates the n-to-p separation bottleneck, reducing the cell active area footprint.

Since a CFET stacks both n- and p-type devices on each other, the transistor provides some benefits. The main benefit is area. In terms of electrostatic control, CFET would be the same as a normal nanowire. Both are gate-all-around architecture.

... and the research goes on ...

MDhere

Top 20

an invite for a cocktail pleaseI’m planning my beach front property already…

JoMo68

Regular

We can lounge in the poolan invite for a cocktail please

alwaysgreen

Top 20

Is that an ogre?Hi SG,

Now you're seeking the forbidden fruit of the Tree of Knowledge.

My serpentine explanation is that ordinary CMOS transistors are built up in layers parallel to the surface of the silicon wafer.

That is, the area of the gate, source, and drain of a field effect transistor (FET) are parallel to the surface, and the thickness is vertical to the surface.

As the density of the CMOS chips reached the limit of the technology (More's law about doubling the number of chips every couple of years), chip engineers needed to find new ways of increasing the number of transistors per wafer.

In a FINFET, the transistor is tipped on its side so the area is vertical to the surface, and the thickness occupies an area of the surface. Because the area is much larger than the thickness, this allows more transistors to be packed in.

Then we got "gate-all-around" (GAA) transistors which improved the performance of the transistors.

https://semiengineering.com/knowledge_centers/integrated-circuit/transistors/3d/gate-all-around-fet/

As the fin width in a finFET approaches 5nm, channel width variations could cause undesirable variability and mobility loss. One promising and futuristic transistor candidate — gate-all-around FET — could circumvent the problem. Considered the ultimate CMOS device in terms of electrostatics, gate-all-around is a device in which a gate is placed on all four sides of the channel. It’s basically a silicon nanowire with a gate going around it.

The comments refer to CFET, which is Complementary FET, a more complex GAA-FET.

https://semiengineering.com/knowledge_centers/integrated-circuit/transistors/3d/cfet/#:~:text=Slated for 2.5nm and beyond, complementary FET (CFET),the transistor stacks n-type wires on each other.

Slated for 2.5nm and beyond, complementary FET (CFET) is a more complex version of a gate-all-around device. Traditional gate-all-around FETs stack several p-type wires on top of each other. In a separate device, the transistor stacks n-type wires on each other.

In CFETs, the idea is to stack both nFET and pFET wires on each other. A CFET could stack one nFET on top of a pFET wire, or two nFETs on top of two pFET wires. This ‘folding’ of the nFET and pFET eliminates the n-to-p separation bottleneck, reducing the cell active area footprint.

Since a CFET stacks both n- and p-type devices on each other, the transistor provides some benefits. The main benefit is area. In terms of electrostatic control, CFET would be the same as a normal nanowire. Both are gate-all-around architecture.

... and the research goes on ...

Stable Genius

Regular

Hi SG,

Now you're seeking the forbidden fruit of the Tree of Knowledge.

My serpentine explanation is that ordinary CMOS transistors are built up in layers parallel to the surface of the silicon wafer.

That is, the area of the gate, source, and drain of a field effect transistor (FET) are parallel to the surface, and the thickness is vertical to the surface.

As the density of the CMOS chips reached the limit of the technology (More's law about doubling the number of chips every couple of years), chip engineers needed to find new ways of increasing the number of transistors per wafer.

In a FINFET, the transistor is tipped on its side so the area is vertical to the surface, and the thickness occupies an area of the surface. Because the area is much larger than the thickness, this allows more transistors to be packed in.

Then we got "gate-all-around" (GAA) transistors which improved the performance of the transistors.

https://semiengineering.com/knowledge_centers/integrated-circuit/transistors/3d/gate-all-around-fet/

As the fin width in a finFET approaches 5nm, channel width variations could cause undesirable variability and mobility loss. One promising and futuristic transistor candidate — gate-all-around FET — could circumvent the problem. Considered the ultimate CMOS device in terms of electrostatics, gate-all-around is a device in which a gate is placed on all four sides of the channel. It’s basically a silicon nanowire with a gate going around it.

The comments refer to CFET, which is Complementary FET, a more complex GAA-FET.

https://semiengineering.com/knowledge_centers/integrated-circuit/transistors/3d/cfet/#:~:text=Slated for 2.5nm and beyond, complementary FET (CFET),the transistor stacks n-type wires on each other.

Slated for 2.5nm and beyond, complementary FET (CFET) is a more complex version of a gate-all-around device. Traditional gate-all-around FETs stack several p-type wires on top of each other. In a separate device, the transistor stacks n-type wires on each other.

In CFETs, the idea is to stack both nFET and pFET wires on each other. A CFET could stack one nFET on top of a pFET wire, or two nFETs on top of two pFET wires. This ‘folding’ of the nFET and pFET eliminates the n-to-p separation bottleneck, reducing the cell active area footprint.

Since a CFET stacks both n- and p-type devices on each other, the transistor provides some benefits. The main benefit is area. In terms of electrostatic control, CFET would be the same as a normal nanowire. Both are gate-all-around architecture.

... and the research goes on ...

Thanks for that simplified explanation @Diogenese.

That’s what I thought too!

The ogre has retired - the odds on his being right are becoming vanishingly small.Is that an ogre?

robsmark

Regular

That’s a little bit sourcy isn’t it?!

cassip

Regular

@chapman89: today I looked at that website of Bosch:

www.bosch-smarthome.com

www.bosch-smarthome.com

Bosch has already been mentioned a few times here. The partners on their website now include Amazon Alexa, Google Assistant, Apple Home Kit, MBUX Mercedes, BMW, ...

www.bosch-smarthome.com

www.bosch-smarthome.com

(Some more partners on the German website:

Regards

cassip

MBUX: Our partner in your Mercedes

Control your Bosch Smart Home using natural speech from your Mercedes – quick and easy with MBUX. Find out more about our smart partner here.

Bosch has already been mentioned a few times here. The partners on their website now include Amazon Alexa, Google Assistant, Apple Home Kit, MBUX Mercedes, BMW, ...

Compatible products and partnerships for your connected home

Bosch Smart Home + Partner: a combination that makes your smart home even more versatile. Learn more about compatible devices and cooperation.

(Some more partners on the German website:

Regards

cassip

cosors

👀

Does he mean Synopsys and not us or are we involved in that? Can any of you explain this to me? I don't understand the connections yet.Works for Mercedes. I wonder who he is referring to?! If it was Brainchip you would imagine that they’ve “reviewed” the IP a while ago, unless they have the new and improved akida containing LSTM?? View attachment 17989

François Piednoel:

"If you think your patent portfolio is impressive, wait to see Synopsys Inc 's"

https://www.linkedin.com/posts/francoispiednoel_if-you-think-your-patent-portfolio-is-impressive-activity-6980764718508503040-CmDH

Diogenese posted:

https://thestockexchange.com.au/threads/brn-discussion-2022.1/post-139109

Similar threads

- Replies

- 3

- Views

- 12K

D

- Replies

- 0

- Views

- 5K

- Replies

- 9

- Views

- 6K

- Replies

- 0

- Views

- 3K