You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

BRN Discussion Ongoing

- Thread starter TechGirl

- Start date

Azzluvstrades

Member

Sorry if has been rooster previously….. Potential competitor here??

techxplore.com

techxplore.com

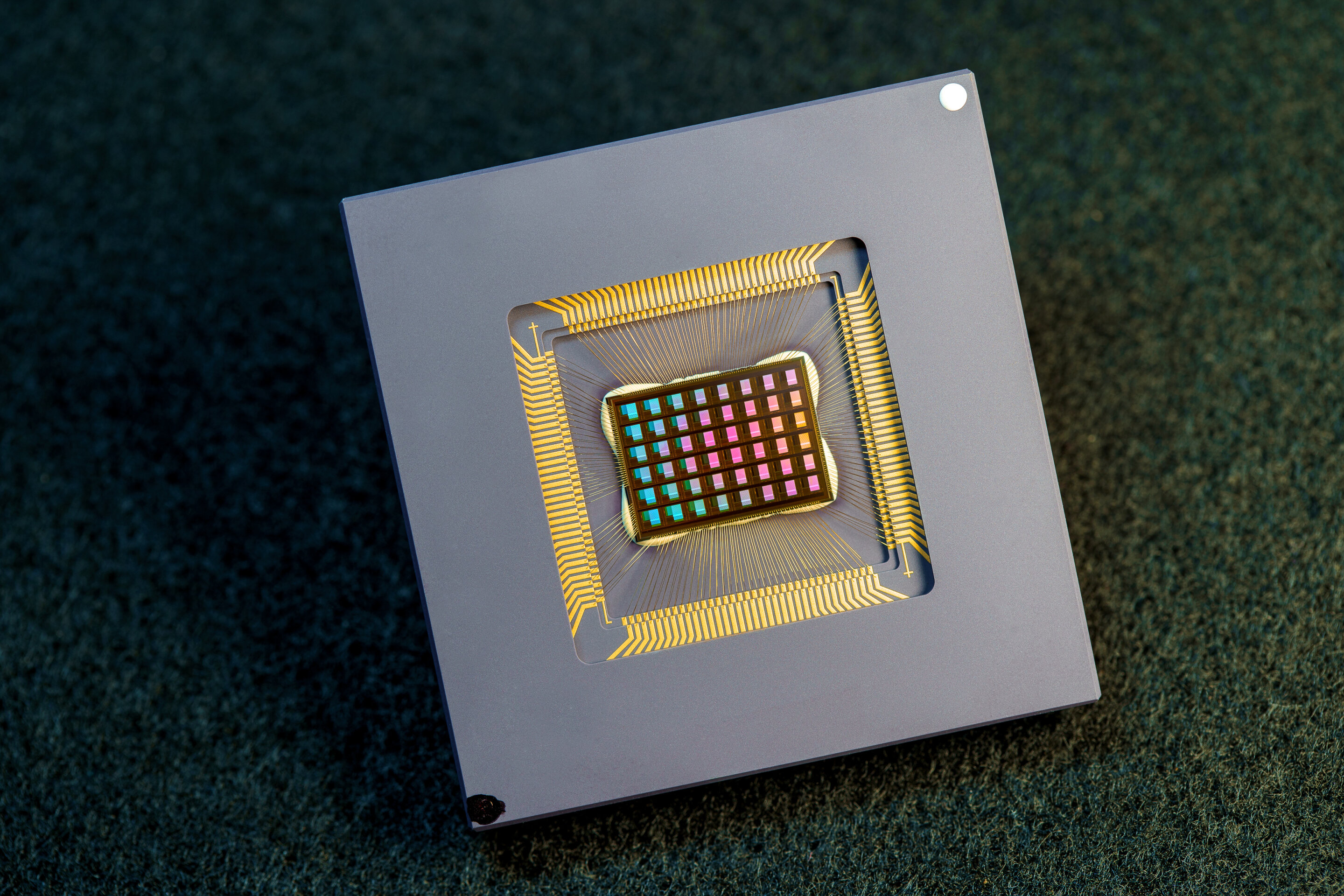

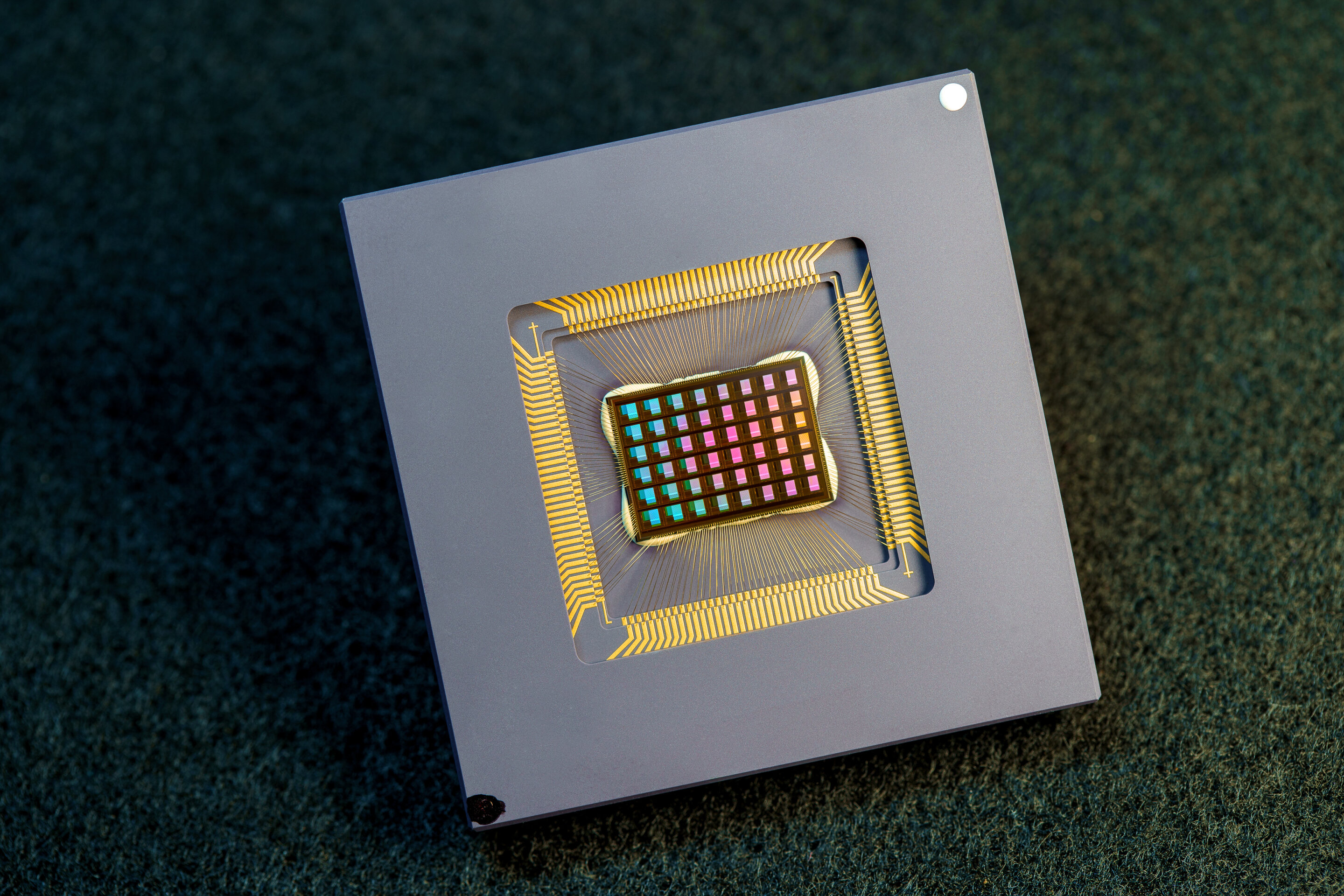

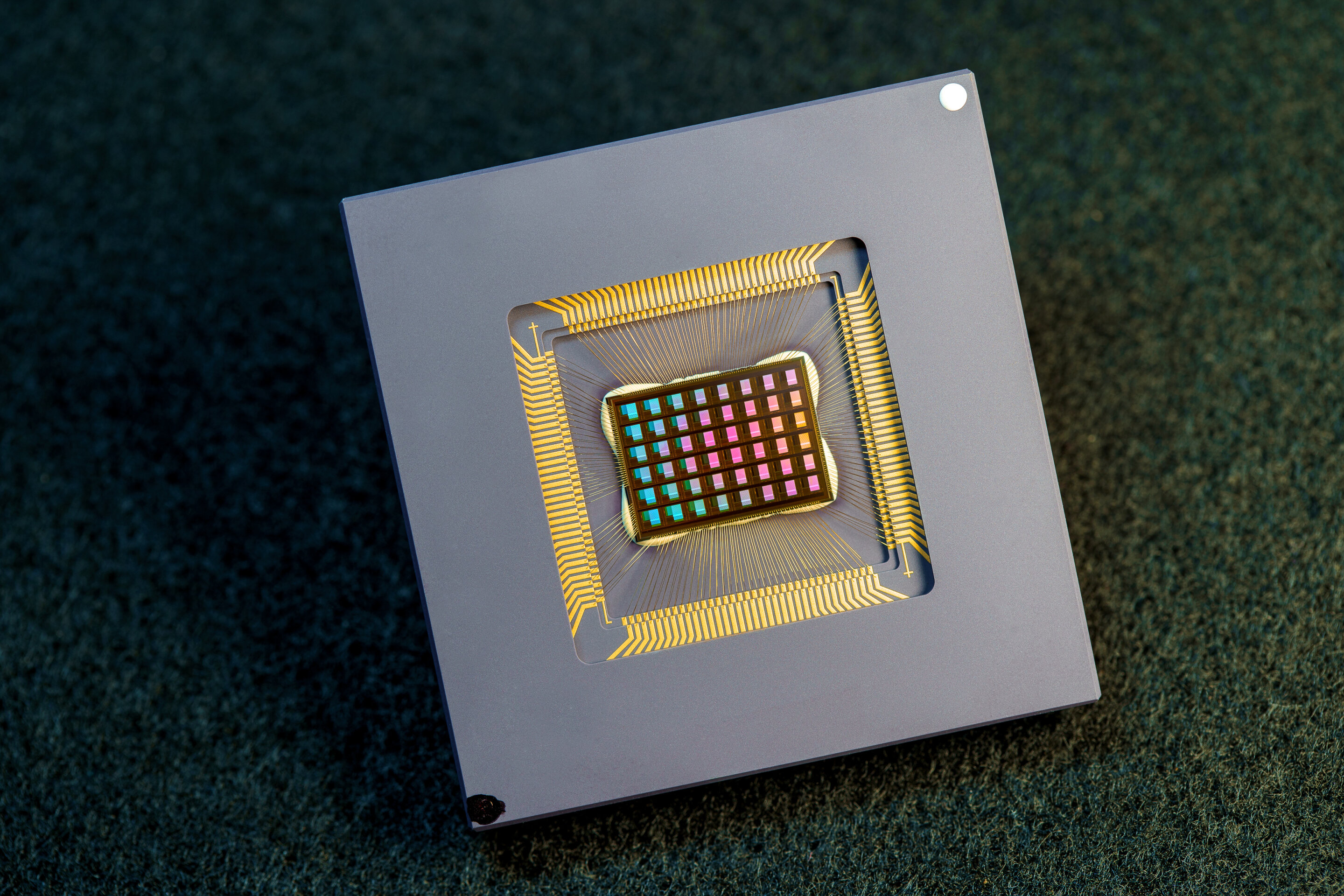

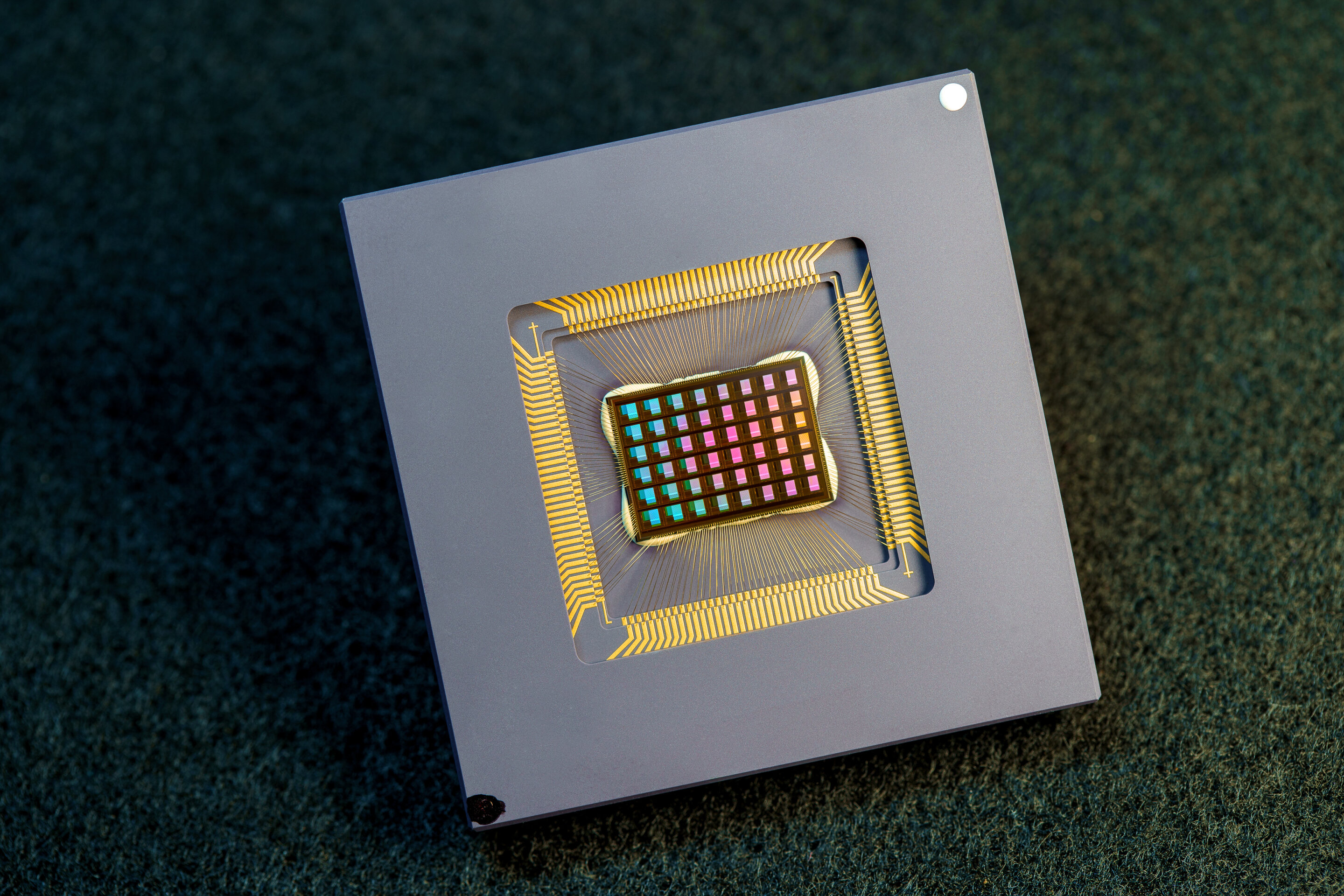

New neuromorphic chip for AI on the edge, at a small fraction of the energy and size of today's computing platforms

An international team of researchers has designed and built a chip that runs computations directly in memory and can run a wide variety of AI applications–all at a fraction of the energy consumed by computing platforms for general-purpose AI computing.

VictorG

Member

Yes, different chip. It will challenge Akida in about.. never..Sorry if has been rooster previously….. Potential competitor here??

New neuromorphic chip for AI on the edge, at a small fraction of the energy and size of today's computing platforms

An international team of researchers has designed and built a chip that runs computations directly in memory and can run a wide variety of AI applications–all at a fraction of the energy consumed by computing platforms for general-purpose AI computing.techxplore.com

Afternoon Azzluvstrades,Sorry if has been rooster previously….. Potential competitor here??

New neuromorphic chip for AI on the edge, at a small fraction of the energy and size of today's computing platforms

An international team of researchers has designed and built a chip that runs computations directly in memory and can run a wide variety of AI applications–all at a fraction of the energy consumed by computing platforms for general-purpose AI computing.techxplore.com

We have looked at this mob , even doused them in flour .

No competition to our Chip was my understanding.

If you go back through several pages here our learned few enlightend us .

Regards,

Esq.

Last edited:

D

Deleted member 118

Guest

Still low volume mate. Lowest volumes we've seen for a while (see chart below).

While it hasn't been nice seeing the price drop from $1.28 near the end of July to where we are at the moment, I am happy to drop on low volume. Remember that for every seller there is a buyer. Hopefully the shares are falling into long term holders hands, reducing liquidity. When the revenue starts to flow, everyone will want a piece and the shares will be trading at a premium!

View attachment 14500

I’m

Happy as I’ve still not my hands on my super yet

Azzluvstrades

Member

Afternoon Azzluvstrades,

We have looked at this mob , even doused them in flour .

No competition to our Chip was my understanding.

If you go back through several pages here our learned few enlightent us .

Regards,

Esq.

Evening Chippers,

Time at posting 5:12 CST.

Last few trades

4:00 - 4:11 $995,460 @ $1.03

4:18:18 , 3162 units @1.05 =$3,320.00 ASX L2 XT

4:18:23, 18506 units @ $1.05 =$19,431.00 ASX L2 XT

( ASX LATE TRADE HEDGE FUND CROSS TRADE )

5:07:52, 18,435 UNITS @ $1.03 = $18,988.00 ASX ET XT

( ASX EXCHANGE TRADED FUNDS CROSSED TRADE ).

Thought we would of seen a little action.

Regards,

Esq.

Time at posting 5:12 CST.

Last few trades

4:00 - 4:11 $995,460 @ $1.03

4:18:18 , 3162 units @1.05 =$3,320.00 ASX L2 XT

4:18:23, 18506 units @ $1.05 =$19,431.00 ASX L2 XT

( ASX LATE TRADE HEDGE FUND CROSS TRADE )

5:07:52, 18,435 UNITS @ $1.03 = $18,988.00 ASX ET XT

( ASX EXCHANGE TRADED FUNDS CROSSED TRADE ).

Thought we would of seen a little action.

Regards,

Esq.

David holland

Regular

I feel the CEO knows the revenue format hence why his confidence around the next AGMI am with you ND. The 3-4 years may be the case if your IP offered an upgrade or variation on what was previously available. But with AKIDA we are re-writing the rule book. I for one believe that that would put a rocket up any timeframe to market.

IMO we are on track, the tech has been validated by several longstanding organisations that sit atop there respective markets. All we have to do now is have the strength to hold, and remember why we bought in, in the first place.

thelittleshort

Top Bloke

In spite of the share price, BrainChip’s allure continues to ascend

Just ticked over to 7000 LinkedIn followers tonight

Just ticked over to 7000 LinkedIn followers tonight

Last edited:

alwaysgreen

Top 20

Now lets see 7,000 million $$ in revenueJust ticked over to 7000 LinkedIn followers tonight

Zedjack33

Regular

I’d settle for something, anything the way we’re running atm.Now lets see 7,000 million $$ in revenue

Deadpool

Akida - Distributed “swarm” architecture

I was going to write something witty, but what a fucking joke, this of course should have been rectify, the minute that you made them aware.I've received a reply from the ASX regarding BRN. It looks like they are coming close to rectifying why BRN has not been included in the daily asx200 top gainers/losers list

View attachment 14497

Don't know if its just bloody incompetence or just some good old fashion organised crime. We all know that we have to put up with the so called legal manipulation of the market, totally designed to shaft us retail investors, let alone the ASX administration blatantly fucking us over as well.

Please excuse the profanities "the devil made me do it" see I can make bullshit excuses to.

Last edited:

S

Straw

Guest

As far as I'm concerned the instos can buy their shares from other instos. Forever.

Get sucked into a nihilistic void to where hedge fund managers retire where they can

try to get one up on each other until the end of time.

Get sucked into a nihilistic void to where hedge fund managers retire where they can

try to get one up on each other until the end of time.

Last edited by a moderator:

wilzy123

Founding Member

I've received a reply from the ASX regarding BRN. It looks like they are coming close to rectifying why BRN has not been included in the daily asx200 top gainers/losers list

View attachment 14497

I also received a very similar response to this after numerous follow-ups by me.

It's annoying, but also pretty hilarious that a company releasing a feature like this on their website would do so without doing adequate user acceptance testing. Makes me wonder where else have they cut corners.

wilzy123

Founding Member

I’d settle for something, anything the way we’re running atm.

Congratulations! You just got that in the last 4C.

stockduck

Regular

Here maybe interesting reading....

His background is very interesting

spectrum.ieee.org

spectrum.ieee.org

Is it possible that Brainchip IP will be used in future developments from Nvidia? I don`t know.

....The DPU can support the ability to offload, accelerate, and isolate data center workloads, reducing CPU and GPU workloads. .......

....

He says Nvidia’s vision for the data center of the future is based on its three chips: CPU, DPU, and GPU.

“These three pillars are connected with a very efficient and high-performance network that was originally developed at Mellanox and is being further developed at Nvidia,” he says.

Development of the BlueField DPUs is now a key priority for Nvidia. It is a data center infrastructure on a chip, optimized for high-performance computing. It also offloads, accelerates, and isolates a variety of networking, storage, and security services. .

.....

What could he mean with the ability of a system on a chip that could "offload and isolate" to get the whole thing more enegy efficient?

(Akida don`t need to be connected to the cloud, it is processing on the chip, right?)

.....

The company is also working closely with the health care industry to develop AI-based technologies. Its supercomputers are helping to identify cancer by generating synthetic data to enable researchers to train their models to better identify tumors. Its AI and accelerated computing products also assist with drug discovery and genome research, Kagan says.

“We are actually moving forward at a fairly nice pace,” he says. “But the thing is that you always need to reinvent yourself and do the new thing faster and better, and basically win with what you have and not look for infinite resources. This is what commitment means.”

His background is very interesting

Nvidia’s CTO on the Future of High-Performance Computing

The company’s Earth-2 supercomputer is taking on climate change

spectrum.ieee.org

spectrum.ieee.org

Is it possible that Brainchip IP will be used in future developments from Nvidia? I don`t know.

....The DPU can support the ability to offload, accelerate, and isolate data center workloads, reducing CPU and GPU workloads. .......

....

He says Nvidia’s vision for the data center of the future is based on its three chips: CPU, DPU, and GPU.

“These three pillars are connected with a very efficient and high-performance network that was originally developed at Mellanox and is being further developed at Nvidia,” he says.

Development of the BlueField DPUs is now a key priority for Nvidia. It is a data center infrastructure on a chip, optimized for high-performance computing. It also offloads, accelerates, and isolates a variety of networking, storage, and security services. .

.....

What could he mean with the ability of a system on a chip that could "offload and isolate" to get the whole thing more enegy efficient?

(Akida don`t need to be connected to the cloud, it is processing on the chip, right?)

.....

The company is also working closely with the health care industry to develop AI-based technologies. Its supercomputers are helping to identify cancer by generating synthetic data to enable researchers to train their models to better identify tumors. Its AI and accelerated computing products also assist with drug discovery and genome research, Kagan says.

“We are actually moving forward at a fairly nice pace,” he says. “But the thing is that you always need to reinvent yourself and do the new thing faster and better, and basically win with what you have and not look for infinite resources. This is what commitment means.”

Last edited:

Morning Potato,When is our full year report due?

Coming up...

1, APPENDIX 4D HALF -YEAR FINANCIAL REPORT.

Last one released 25th August 2021.

2, APPENDIX 4C & QUARTERLY ACTIVITIES REPORT for the period ended 30th September 2022.

Last one put out on 21st October 2021.

3, APPENDIX 4E PRELIMINARY FINAL REPORT. Up to December 31st 2022

&

ANNUAL REPORT 2022.

Last one released on 23/2/2021

Regards,

Esq.

Cyw

Regular

I sure hope the annual report contains a bit more than a few lines of no information.Morning Potato,

Coming up...

1, APPENDIX 4D HALF -YEAR FINANCIAL REPORT.

Last one released 25th August 2021.

2, APPENDIX 4C & QUARTERLY ACTIVITIES REPORT for the period ended 30th September 2022.

Last one put out on 21st October 2021.

3, APPENDIX 4E PRELIMINARY FINAL REPORT. Up to December 31st 2022

&

ANNUAL REPORT 2022.

Last one released on 23/2/2021

Regards,

Esq.

Morning Chippers,

From the weekend financial paper..

1, Article: Lithium miners gain amid meme stock frenzy .

Author: Alek Vickovic.

Market darlings

Top 10 most bought Australian shares on Superhero.

Brainchip ranked number 7 in July.

2, Article: AI, Mental health , China: Packer plots his return.

Author: Mark Di Stefano

* no mention of Brainchip directly.

Snippet from above article... packer said the family would be returning to Australia in March for his next act.

With his intended return to Australian public life, Packer could be seeking redemption rather than revenge. He plans to work and invest in companys and projects linked to his areas of intrest : artificial intelligence, mental health and Australia's relationship with China.

"I don't see myself being an Australian company director, " he told the Financial Review. " Doesn't mean I won't buy shares in Australian companies. "

3, Article: The incredible hulk. Hummers mighty , sprightly EV.

Author: Tony Davis.

* nothing directly Brainchip, possibly for the super sleuths.

The vehicle introduces GM's Ultium EV platform and battery system, with the claim it can add 160 kilometres of range with 10 minutes of charging.

Weighs 4082 kg

Range 530 km

Three electric motors with 210kWh battery pack.

$112,595.00 USD price tag.

Regards,

Esq.

From the weekend financial paper..

1, Article: Lithium miners gain amid meme stock frenzy .

Author: Alek Vickovic.

Market darlings

Top 10 most bought Australian shares on Superhero.

Brainchip ranked number 7 in July.

2, Article: AI, Mental health , China: Packer plots his return.

Author: Mark Di Stefano

* no mention of Brainchip directly.

Snippet from above article... packer said the family would be returning to Australia in March for his next act.

With his intended return to Australian public life, Packer could be seeking redemption rather than revenge. He plans to work and invest in companys and projects linked to his areas of intrest : artificial intelligence, mental health and Australia's relationship with China.

"I don't see myself being an Australian company director, " he told the Financial Review. " Doesn't mean I won't buy shares in Australian companies. "

3, Article: The incredible hulk. Hummers mighty , sprightly EV.

Author: Tony Davis.

* nothing directly Brainchip, possibly for the super sleuths.

The vehicle introduces GM's Ultium EV platform and battery system, with the claim it can add 160 kilometres of range with 10 minutes of charging.

Weighs 4082 kg

Range 530 km

Three electric motors with 210kWh battery pack.

$112,595.00 USD price tag.

Regards,

Esq.

Similar threads

- Replies

- 3

- Views

- 12K

D

- Replies

- 0

- Views

- 5K

- Replies

- 9

- Views

- 6K

- Replies

- 0

- Views

- 3K